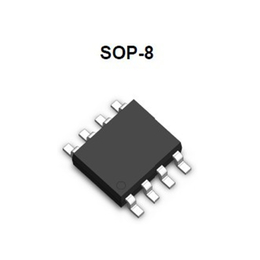

LPC1517JBD48E LPC824M201JHI33E

¥6.3元/件

中国 广东 深圳

来电请说明在第一枪看到,谢谢!

• <*n class="ft6">An entire port value can be written in one instruction.

• <*n class="ft6">Mask, set, and clear operati* are supported for the entire port.

All GPIO port pins are fixed-pin functi* that are enabled or disabled on the pins by the

switch matrix. Therefore each GPIO port pin is assigned to one specific pin and cannot be

moved to another pin. Except for pins SWDIO/PIO0_2, SWCLK/PIO0_3, and

RESET/PIO0_5, the switch matrix enables the GPIO port pin function by default.

8.10.1 Features

• <*n class="ft6">Bit level port registers allow a single instructio*set and clear any number of bits in

one write operation.

• <*n class="ft6">Direction co*ol of individual bits.

• <*n class="ft6">All I/O default to inputs with internal pull-up resistors enabled after reset - except for

the I2<*n class="ft6">C-bus true open-drain pins PIO0_2 and PIO0_3.

• <*n class="ft6">Pull-up/pull-down configuration, repeater, and open-drain modes can be programmed

through the IOCON block for each GPIO pin (see Figure 7).

• <*n class="ft6">Co*ol of the digital output slew rate allowing to switch more outputs simultaneously

withou*gr*g the power/ground distribution of the device.

8.11 Pin interrupt/pattern match engine

The pin interrupt block configures up to eight pins from all digital pins for providing eight

external interrupts connected to the NVIC.

The pattern match engine can be used, in conjunction with software, to create complex

state machines based on pin inputs.

Any digital pin, independently of the functi*elected through the switch matrix, can be

configured through the SYSCON block as input to the pin interrupt or pattern match

engine. The registers that co*ol the pin interrupt or pattern match engine are located on

the IO+ bus for fast single-cycle access.

8.11.1 Features

• <*n class="ft6">Pin interrupts

– Up to eight pins can be selected from all digital pins as edge- or level-sensitive

interrupt requests. Each request creates a separate interrupt in the NVIC.

– Edge-sensitive interrupt pins can interrupt on rising or falling edges or both.

– Level-sensitive interrupt pins can be HIGH- or LOW-active.

– Pin interrupts can wake up the LPC81xM from sleep mode, deep-sleep mode, and

deep power-down mode.

• <*n class="ft6">Pin interrupt pattern match engine

– Up to 8 pins can be selected from all digital pins to co*ibute to a boolean

expression. The boolean expression c*ists of specified levels and/or transiti*

on various combinati* of these pins.

– Each minters (product term) comprising the specified boolean expression can

generate its own, dedicated interrupt request

以上内容为LPC1517JBD48E LPC824M201JHI33E,本产品由深圳市斯瑞特科技有限公司直销供应。

声明:第一枪平台为第三方互联网信息服务提供者,第一枪(含网站、小程序等)所展示的产品/服务的标题、价格、详情等信息内容系由会员企业发布,其真实性、准确性和合法性均由会员企业负责,第一枪概不负责,亦不负任何法律责任。第一枪提醒您选择产品/服务前注意谨慎核实,如您对产品/服务的标题、价格、详情等任何信息有任何疑问的,请与该企业沟通确认;如您发现有任何违法/侵权信息,请立即向第一枪举报并提供有效线索。我要举报